# A wide input range, external capacitor-less LDO with fast transient response

Mali Gao<sup>1</sup>, Xiaowu Cai<sup>1</sup>, Weiwei Yan<sup>1</sup>, Haitao Zhao<sup>1</sup>, Ruirui Xia<sup>1</sup>, and Yuexin Gao<sup>1</sup>

<sup>1</sup>Institute of Microelectronics pf Chinese Academy of Sciences

October 24, 2022

## Abstract

A high-voltage, external capacitor-less low-dropout regulator (HVLDO) with a transient enhancement loop is presented in this work. The proposed HVLDO is designed with high withstand voltage LDMOS transistors and a transient enhancement loop is proposed to properly inject or sink current to/from the gate and output nodes of the power transistors to achieve fast transient response under wide load range conditions and high stability. This HVLDO is fabricated in 0.5  $\mu$ m SOI BCD process with an active area of 0.29 mm2. It operates over an input voltage range of 5.2 to 20 V, provides an output voltage of 5 V and a maximum load of 100 mA, while supporting load capacitances from 0 pF to 1  $\mu$ F. Measurements show that this design has a line regulation of 0.88 mV/V and a load regulation of 0.22 mV/mA. The proposed HVLDO features fast line transient response of 60/20 mV@9.8 V/ $\mu$ s, fast load transient response of 30/70 mV@100 mA/ $\mu$ s, and recovery time of 2  $\mu$ s without external capacitors. Compared with the prior art, this work achieves the best transient FOM of 12.19 fs.

A wide input range, external capacitor-less LDO with fast transient response

Mali Gao<sup>1, 2, 3</sup>, Xiaowu Cai<sup>1, 3,\*</sup>, Weiwei Yan<sup>1, 3</sup>, Haitao Zhao<sup>1, 3</sup>, Ruirui Xia<sup>1, 2, 3</sup>, Yuexin Gao<sup>1, 2, 3</sup>

<sup>1</sup>Institute of Microelectronics, Chinese Academy of Sciences, Beijing, 100029, China

<sup>2</sup>University of Chinese Academy of Sciences, Beijing, 100029, China

<sup>3</sup>Key Laboratory of Science and Technology on Silicon Devices, Chinese Academy of Sciences, Beijing, 100029, China

\* Email: caixiaowu@ime.ac.cn

A high-voltage, external capacitor-less low-dropout regulator (HVLDO) with a transient enhancement loop is proposed HVLDO is designed with high withstand voltage LDMOS transistors and a transient enhancement loop is proposed to properly inject or sink current to/from the gate and output nodes of the power transistors to achieve fast transient response under wide load range conditions and high stability. This HVLDO is fabricated in 0.5  $\mu$ m SOI BCD process with an active area of 0.29 mm<sup>2</sup>. It operates over an input voltage range of 5.2 to 20 V, provides an output voltage of 5 V and a maximum load of 100 mA, while supporting load capacitances from 0 pF to 1  $\mu$ F. Measurements show that this design has a line regulation of 0.88 mV/V and a load regulation of 0.22 mV/mA. The proposed HVLDO features fast line transient response of 60/20 mV@9.8 V/ $\mu$ s, fast load transient response of 30/70 mV@100 mA/ $\mu$ s, and recovery time of 2  $\mu$ s without external capacitors. Compared with the prior art, this work achieves the best transient FOM of 12.19 fs.

*Introduction:* In recent years, battery-powered equipment and portable electronic products such as automotive and telecom electronics have developed rapidly, hence the demand for high voltage power management systems is also increasing. Compared with switching power supply regulators and charge pump power supply regulators, low dropout linear regulators have the advantages of small area, small ripple, high power supply noise rejection ratio and fewer external components, which make them widely used in high-precision electronic products [1].

However, traditional LDOs have a narrow input supply range (typically 2-5 V) and require external output capacitors in the  $\mu$ F range for improved transient response and good stability. But this requires extra external pins and cannot be integrated into the whole chip. To remove external components and reduce system size, capacitorless LDOs are proposed in [2-7]. But all previous LDOs have trade-offs between wide input and load current ranges, the need for large off-chip capacitors, and output transient response. In this letter, a capacitorless HVLDO with transient enhancement loop is proposed. Benefiting from the transient enhancement loop, the proposed LDO has optimized line and load regulation performance and fast load transient and line transient response.

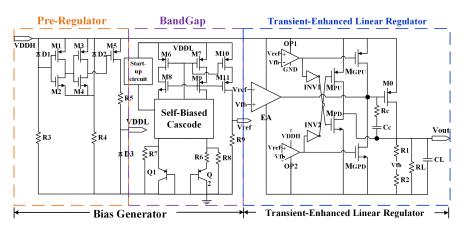

LDO design: Fig. 1 shows the topology of the proposed HVLDO. The pre-regulator circuit is designed to power the bandgap reference circuit to improve PSR. The bandgap reference provides proper biasing for the LDO and achieves a temperature coefficient of 13.15 ppm/°C, over a wide temperature range of -40-150°C. Transient-enhanced linear regulator is the core part, which can output regulated voltages during load and supply voltage transients.

### Fig. 1 Topology of the proposed HVLDO.

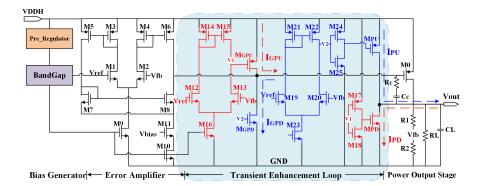

The circuit implementation of the proposed transient enhancement linear regulator is presented in Fig. 2, including the bias generation circuit, error amplifier, transient enhancement loop, and power output stage. Bias generation circuit generates proper bias voltage and current for LDO. The error amplifier detects the change of the output voltage through the feedback resistors R1 and R2, compares Vfb with the reference voltage Vref, then controls the gate voltage of the power transistor M0 to stabilize the output voltage. In particular, the design proposes a transient enhancement loop, which provides an additional fast control loop for the gate of M0 while acting as an active capacitor to provide transient inject or sink current to/from the output point, enhancing transient response without off-chip capacitors.

#### Fig. 2 Schematic of the proposed HVLDO with transient enhancement loop.

*Error Amplifier:* The error amplifier is a symmetrical transconductance amplifier (OTA) consisting of M1-M11. M10 and M11 provide higher DC bias for the source stage of M8, so that the output of the OTA can drive the P-type power output transistor M0 with a suitable common-mode voltage. The power output stage consists of power transistor M0, feedback resistor network R1, R2 and 5 pF Miller compensation capacitor Cc and zeroing resistor Rc. The output power transistor M0 has an aspect ratio of 10 mm/360 nm to provide 100 mA at a voltage drop of 200 mV.  $C_L$  and  $R_L$  are the load capacitance and load resistance. The error amplifier detects the change of the output voltage and compares Vfb with the reference voltage Vref, then controls the gate voltage of the M0 to stabilize the output voltage.

Transient Enhancement Loop: The circuit implementation of the proposed transient enhancement loop is shown in Fig. 2, consisting of 18 transistors M12-M25,  $M_{PU}$ ,  $M_{PD}$ ,  $M_{GPU}$ ,  $M_{GPD}$ , including the M0 gate transient enhancement control loop and output grade active capacitors. Specifically, the two pairs of operational amplifiers M12-M16 and M19-M23 detect the output Vout change through the feedback point Vfb. The OTA control transistor  $M_{GPU}$  (or  $M_{GPD}$ ) injects (or pulls out) a transient current  $I_{GPU}$  (or  $I_{GPD}$ ) to the gate of M0, thereby pulling the gate voltage of M0 high (or low). The gate transient enhancement control loop of M0 can shorten the transient response time, replace the traditional analog buffer to minimize the quiescent current. The active capacitor shares the OTA with the gate transient control loop. Inverter M17-18 (or M24-25) controls  $M_{PD}$  (or  $M_{PU}$ ) to pull out (or inject) the transient current  $I_{PD}$  (or  $I_{PU}$ ) out of the LDO output for instantly suppressing  $\Delta$ Vout, which achieves the transient response enhancement.

The GBW of the transient enhancement circuit is designed to be higher than that of the error amplifier to meet the corresponding needs of fast transients. Set the width to length ratio of M17-18 and M24-25 in

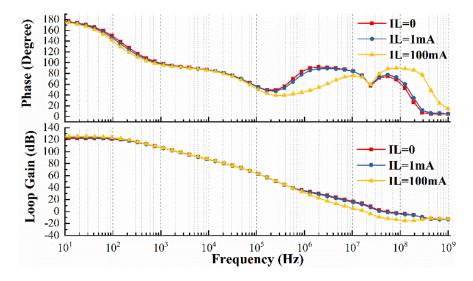

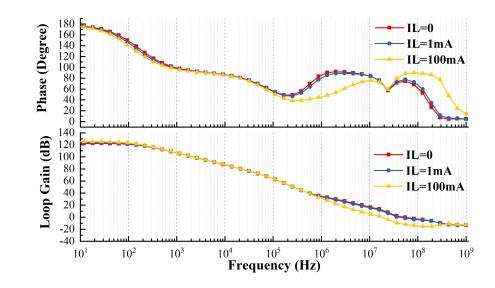

Fig. 2 to adjust their inversion thresholds (corresponding to INV1 and INV2 in Fig. 1) so that  $M_{PU}$  and  $M_{PD}$  are turned off in steady state and only work for transient response , which can improve stability and reduce power consumption. Set the size of  $M_{PU}$  and  $M_{PD}$  to 60:1 of M0 to avoid excessive transient current compensation. In order to verify the stability of the HVLDO, the stability of the HVLDO under different load conditions is simulated, and the results are shown in Fig. 3. It can be seen that PM is 74.2 deg@0 mA, 74.5 deg@1 mA and 68.4 deg@100 mA. The circuit has good stability under all load conditions.

Fig. 3 Stability simulation results under different load conditions.

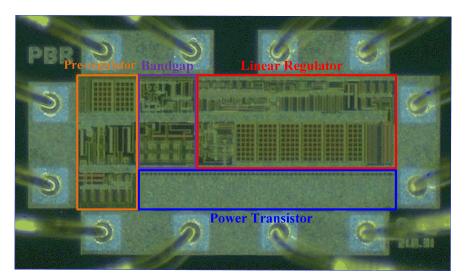

*Measurement results:* The proposed HVLDO was implemented in 0.5  $\mu$ m SOI BCD process with an active area of 835 $\mu$ m\*347 $\mu$ m (without pads) as shown in the chip micrograph in Fig. 4. This HVLDO delivers a maximum load of 100 mA. The ground current of this HVLDO is 243.8  $\mu$ A when the load current increases from 0 to 100 mA. The peak current efficiency achieves 99.75%.

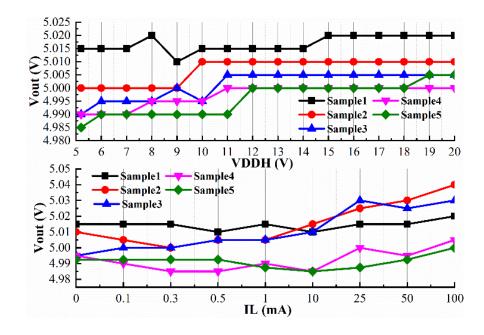

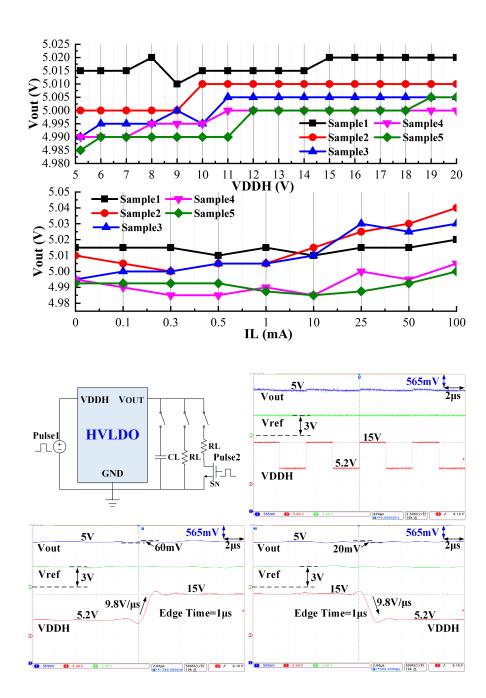

Fig. 5 shows the measurement results of line regulation

Fig. 4 Chip micrograph of the proposed HVLDO.

Fig. 5 Measured line regulation results ( $I_L=0mA$ ) and load regulation results (VDDH=10V) of five samples. Fig. 6 Transient performance test setup and the measured line transient response at  $I_L = 50mA$  and  $C_L = 0$  pF.

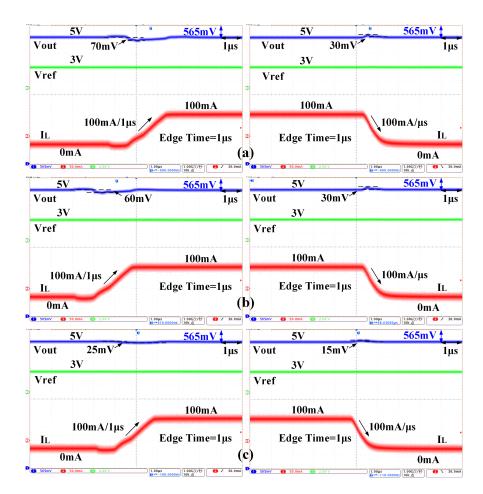

Fig. 7 Measured load transfert respectively with "DDH = 20" (a) "\_A = 0 pd,  $T_{E\delta\gamma\epsilon} = 1 \mu\varsigma$ , (b) "\_A = 100 rd,  $T_{E\delta\gamma\epsilon} = 1 \mu\varsigma$ , (c) "\_A = 22  $\mu\Phi$ ,  $T_{E\delta\gamma\epsilon} = 1 \mu\varsigma$ .

and load regulation for 5 samples.  $I_L = 0mA$ , VDDH varies between 5.2-20 V, the average value of  $\Delta$ Vout is 13 mV, and the line regulation reaches 0.88mV/V. VDDH=10V,  $I_L$  varies between 0-100mA, the average value of  $\Delta$ Vout is 22 mV, and the load regulation is 0.22 mV/mA.

Fig. 6 shows the transient performance test setup and the measured line transient response, it can be obtained that this design has a fast line transient response with overshoot/undershoot of 60/20mV under the line-step slew rate of 9.8V/µs.

Fig. 7 presents the load transient response of the proposed HVLDO under different conditions. It can be observed that I<sub>L</sub> jumps from 0-100mA with an edge time of  $T_{Edge} = 1 \ \mu s$ . When the load capacitances C<sub>L</sub> of (a), (b) and (c) are 0 pF, 1 nF and 1  $\mu$ F, respectively, the overshoot /undershoot voltages were 30/70 mV, 30/60 mV and 15/25 mV, respectively. In conclusion, the proposed HVLDO has a fast transient response in the load capacitance range of 0-1  $\mu$ F.

| Parameter         | [2], 2019 | [3], 2021  | [4], 2020 | [5], 2014 | This work  |

|-------------------|-----------|------------|-----------|-----------|------------|

| Tech (µm)         | 0.18      | 0.4        | 0.18      | 0.6       | 0.5        |

| Area $(mm^2)$     | 0.18      | 0.544      | 0.184     | 0.3       | 0.29       |

| $V_{in}$ (V)      | 3.3       | 4.3-24     | 5 - 12    | 4-40      | 5.2 - 20   |

| $V_{out}(V)$      | 2.8       | 3.3        | 4         | 2.5 - 5   | 5          |

| Vdo (mV)          | 500       | 1000       | 1000      | >200      | <b>200</b> |

| TC (ppm/)         | NA        | 185        | 30        | NA        | 13.15      |

| $I_{LOAD}$ (mA)   | 100       | 50         | 50        | 30        | 100        |

| $I_Q$ ( $\mu A$ ) | 32        | $3.2^*$    | $8.2^{*}$ | $8^*$     | 243.8      |

| LNR (mV/V)        | 5.6       | $0.56^{*}$ | 0.34      | 1.38      | 0.88       |

Table 1. Comparation with the state-of-the-art

| Parameter                  | [2], 2019        | [3], 2021 | [4], 2020 | [5], 2014 | This work |

|----------------------------|------------------|-----------|-----------|-----------|-----------|

| LDR (mV/mA)                | 0.028            | 0.26      | NA        | 0.335     | 0.22      |

| LNTR (mV)                  | 65/75            | NA        | NA        | NA        | 60/20     |

| $T_{Edge, LNTR} (\mu s/V)$ | 10/3 - 3.5       | NA        | NA        | NA        | 1/5.2-15  |

| LDTR (mV)                  | 170/640          | NA        | NA        | 83/103    | 30/70     |

| $T_{Edge, LDTR} (\mu s/A)$ | $0.1/100 { m m}$ | NA        | NA        | 1/100m    | 1/100m    |

| Setting Time $(\mu s)$     | 52               | NA        | NA        | >10       | 2         |

| PSR (dB) at $100kHz$       | NA               | NA        | >-40      | NA        | -49       |

| $C_{TOT}$ (pF)             | 100              | 1000      | 2200      | 1000      | 5         |

| FOM (fs)                   | 25.92            | NA        | NA        | 1653.3    | 12.19     |

<sup>\*</sup>Minimum value

Table 1 provides a performance comparison with the state-of-the-art. Among all products, the proposed HVLDO has the fastest transient response, short recovery time, lower line regulation and fastest line transient response without off-chip capacitors. The design provides a maximum output current of 100mA and an output voltage of 5V over a wide supply range of 5.2-20V and achieves a temperature coefficient of 13.15 ppm/°C. To compare various regulators implemented in different technologies, an FOM is adopted from [7] and [8]. The smaller the FOM, the better the transient response achieved by the LDO. As shown in Table 1, the proposed HVLDO achieves the smallest FOM factor among all these products.

$$FOM = K * \frac{C_{\text{TOT}} \times V_{\text{out}} \times I_Q}{I_{\text{LOAD}}^2} \# (1)$$

$$K = \frac{\Delta t \text{ used in the measurement}}{\text{the maximum } \Delta t \text{ in the design for comparison}} \# (2)$$

Conclusions: This work presents a wide input range, external capacitor-Less LDO based on a transient enhancement loop. The proposed HVLDO can provide a regulated 5 V output over an input voltage range of 5.2-20 V with a maximum load of 100 mA, line regulation of 0.88 mV/V, load regulation of 0.22 mV/mA, PM over 68.4 deg and PSR of -49 dB@100 kHz for all load conditions. In particular, the design features fast line transient response of 60/20mV over/undershoot voltage and fast transient response of 30/70mV over/undershoot voltage and 2 µs setting time, which achieves the transient FOM of 12.19 fs. In summary, the proposed HVLDO is suitable for applications in high-voltage power supplies.

Acknowledgments: This work is supported by the National Natural Science Foundation of China (Grant No.61874135).

*Conflict of interest:* No financial interests/personal relationships need to be considered as potential competing interests.

*Data availability statement:* The data that support the findings of this study are available from the corresponding author upon reasonable request.

? 2022 The Authors. *Electronics Letters* published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### References

S.-W. Hong and G.-H. Cho, "High-Gain Wide-Bandwidth Capacitor-Less Low-Dropout Regulator (LDO) for Mobile Applications Utilizing Frequency Response of Multiple Feedback Loops," IEEE Trans. Circuits Syst. I, vol. 63, no. 1, pp. 46–57, Jan. 2016, doi: 10.1109/TCSI.2015. 2512702.

- Z. Guo et al., "Topological Classification-Based Splitting-Combining Methodology for Analysis of Complex Multi-Loop Systems and Its Application in LDOs," IEEE Trans. Power Electron., vol. 34, no. 7, pp. 7025–7039, Jul. 2019, doi: 10.1109/TPEL. 2018.2876138.

- Y. Cao and Z. Wen, "A Wide Input Voltage Range, Low Quiescent Current LDO Using Combination Structure of Bandgap and Error Amplifier," in 2021 6th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, Oct. 2021, pp. 240–245. doi: 10.1109/ICICM54364.2021.9660242.

- S. Liu, M. Zhao, Z. Yang, and X. Wu, "Design of self-referenced wide input voltage range LDO using enhanced current mirror buffer and improved lead compensation," IEICE Electron. Express, vol. 17, no. 11, pp. 20200120–20200120, Jun. 2020, doi: 10.1587/elex.17. 20200120.

- X. Yang, T. Lu, J. Zhang, and Y. Zong, "A Low-Quiescent Current Low-Dropout Regulator with Wide Input Range," IJEEE, vol. 3, no. 3, 2014, doi: 10.12720/ijeee.3.3.182-186.

- 6. J. Pérez-Bailon, A. Marquez, B. Calvo, N. Medrano, and P. A. Martinez, "Fast-transient high-performance 0.18 μm CMOS LDO for battery-powered systems," Electron. lett., vol. 53, no. 8, pp. 551–552, Apr. 2017, doi: 10.1049/el.2016.4541.

- H. Fan et al., "An External Capacitor-Less Low-Dropout Voltage Regulator Using a Transconductance Amplifier," IEEE Trans. Circuits Syst. II, vol. 66, no. 10, pp. 1748–1752, Oct. 2019, doi: 10.1109/TCSII.2019.2921874.

- D. Mandal, C. Desai, B. Bakkaloglu, and S. Kiaei, "Adaptively Biased Output Cap-Less NMOS LDO With 19 ns Settling Time," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 2, pp. 167–171, 2019, doi: 10.1109/TCSII.2018.2842642.

# Hosted file

Table 1. Comparation with the state-of-the-art.docx available at https://authorea.com/ users/517127/articles/591773-a-wide-input-range-external-capacitor-less-ldo-with-fasttransient-response