## Threshold voltage instability and device failure mechanism of p-GaN gate HEMTs under repetitive short-circuit stress

Jian Zhang<sup>1</sup>, Chaowu Pan<sup>1</sup>, Ning Yang<sup>1</sup>, Kuangli Chen<sup>2</sup>, and Qi Zhou<sup>1</sup>

<sup>1</sup>University of Electronic Science and Technology of China <sup>2</sup>University of Electronic Science and Technology of China (UESTC)

February 22, 2024

## Abstract

In this letter, the underlying physics of threshold voltage (Vth) instability and the eventual device failure mechanism of 100V Schottky p-GaN gate high electron mobility transistors (HEMTs) under repetitive short-circuit (SC) stress with varied drain voltage (VDD= 40-70V) and SC pulse duration (TSC=10  $\mu$ s & 20  $\mu$ s) is studied. In the lenient SC stress with lower SC energy (e.g. SC stress @ VGS=6 V, VDD=40-70 V, TSC=10  $\mu$ s), the devices exhibit significantly positive Vth shift while the Vth instability shows positive dependence with the stressed drain voltage and the repetitive SC pulses. For device stressed at VDD=70 V with 150 SC pulses, a substantial  $\Delta$ Vth as high as +0.68 V is observed. Such a prominent Vth instability is induced by the electron trapping in the p-GaN gate region during the SC events, which also results in the suppressed gate and drain leakage current after SC stress. In the more stringent SC stress (VGS=6 V, VDD=70 V, TSC=20  $\mu$ s) with much higher corresponding SC energy, the device failed due to the drain electrode burned out initiated by the significantly high SC energy during the SC events.

Threshold voltage instability and device failure mechanism of p-GaN gate HEMTs under repetitive shortcircuit stress

Jian Zhang<sup>1</sup>, Chaowu Pan<sup>1</sup>, Ning Yang<sup>1</sup>, Kuangli Chen<sup>1</sup>, and Qi Zhou<sup>1,2</sup>,

<sup>1</sup> University of Electronic Science and Technology of China (UESTC), Chengdu, P.R. China,

<sup>2</sup>Institute of Electronic and Information Engineering, UESTC, Dongguan, Guangdong, P.R. China.

Email: zhouqi@uestc.edu.cn

In this letter, the underlying physics of threshold voltage ( $V_{\rm th}$ ) instability and the eventual device failure mechanism of 100V Schottky p-GaN gate high electron mobility transistors (HEMTs) under repetitive shortcircuit (SC) stress with varied drain voltage ( $V_{\rm DD}$ = 40-70V) and SC pulse duration ( $T_{\rm SC}$ =10 µs & 20 µs) is studied. In the lenient SC stress with lower SC energy (e.g. SC stress @ $V_{\rm GS}$ =6 V,  $V_{\rm DD}$ =40-70 V,  $T_{\rm SC}$ =10 µs), the devices exhibit significantly positive  $V_{\rm th}$  shift while the  $V_{\rm th}$  instability shows positive dependence with the stressed drain voltage and the repetitive SC pulses. For device stressed at  $V_{\rm DD}$ =70 V with 150 SC pulses, a substantial  $\Delta V_{\rm th}$  as high as +0.68 V is observed. Such a prominent  $V_{\rm th}$  instability is induced by the electron trapping in the p-GaN gate region during the SC events, which also results in the suppressed gate and drain leakage current after SC stress. In the more stringent SC stress ( $V_{\rm GS}$ =6 V,  $V_{\rm DD}$ =70 V,  $T_{\rm SC}$ =20 µs) with much higher corresponding SC energy, the device failed due to the drain electrode burned out initiated by the significantly high SC energy during the SC events.

Introduction: In recent years, owing to its superior power performance, the p-GaN gate HEMTs have been commercialized and used in fast charger, LiDAR, and data-center etc. However, the device stability is still a challenge and the underlying physics responsible for the device instability as well as the device failure mechanism are of great interests for further improvement of the device stability to deliver stable and high-power performance of GaN power electronics. In the high frequency power applications, such as PFC converter and LLC resonant circuit, short circuit (SC) robustness is important for the stable and safe operation of power circuits. The SC fault may occur due to the failure or short in the load, faulty gate control signals, crosstalk in a phase-leg circuit [1], [2] etc. During the SC events, the device simultaneously undergoes a high bus voltage and large SC current, such a harsh condition may result in significant device degeneration of GaN power conversion systems. Hence, investigating the device instability and failure mechanism is of great importance to improve the SC stability of p-GaN gate HEMTs.

Recently, the SC characteristics of 600V/650V high voltage p-GaN gate HEMTs under different SC conditions have been investigated [3]-[6]. The high voltage HEMTs exhibit weak repetitive SC capability since the high SC energy generates significant heat during the SC events which leads to prominent mechanical stress and

then results in fatigue or fracture failure [4]. However, the SC characteristics and device instability of 100 V low-voltage p-GaN gate HEMTs are rarely reported [7]. Particularly, the ultimate device failure mechanism under SC events is still lacking up to date.

In this work, by conducting the repetitive SC stress with up to 150 pulse cycles and varied stress  $V_{\rm DD}$  and  $T_{\rm SC}$ , the  $V_{\rm th}$  instability during the evolution of the SC stress is recorded and the underlying mechanism is studied. By further enhancing the stress condition with higher SC energy, the eventual device failure is observed and the failure mechanism is revealed by studying the SC waveform and chip microscopy. The experimental results show that the studied 100 V p-GaN gate HEMTs feature quite different SC characteristics from the reported 600/650 V p-GaN gate HEMTs [3]-[6].

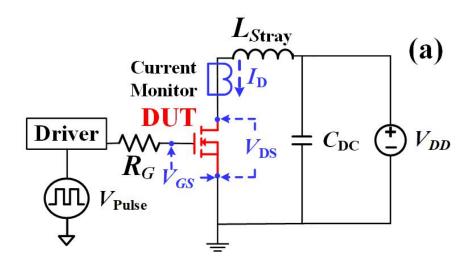

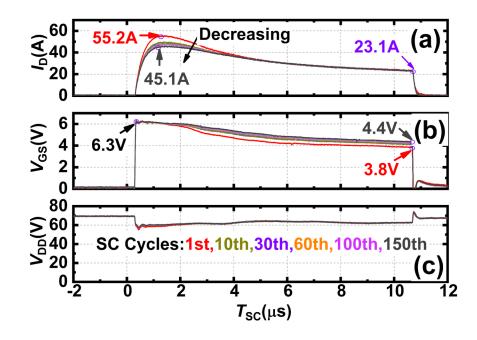

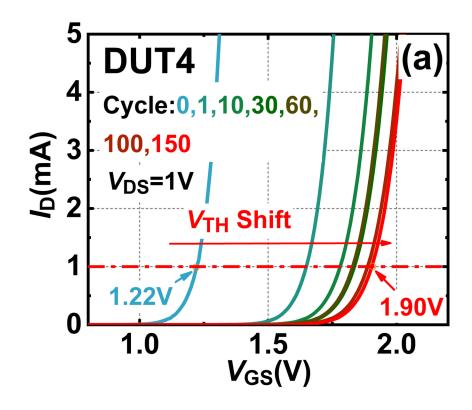

Experiments and discussion: The device studied is the 100 V/25 m $\Omega$  Schottky-type p-GaN gate HEMTs commercial product. The device structure can be found in our previous report [7]. Fig. 1 (a) plots the SC measurement circuit. Fig.1 (b) shows the repetitive SC stress and device characterization strategy. The devices were stressed by up to 150 SC pulses that is 50% higher than our previous report [7], while the device characteristics were respectively recorded after the  $1^{st}$ ,  $10^{th}$ ,  $30^{th}$ ,  $60^{th}$ ,  $100^{th}$ , and  $150^{th}$  SC pulse during the repetitive SC evolution. Fig. 2 plots the typical repetitive SC waveforms of  $V_{\rm GS}=6$  V,  $V_{\rm DD}=70$ V and  $T_{\rm SC}=10 \ \mu s$  for the  $1^{st}$ ,  $10^{th}$ ,  $30^{th}$ ,  $60^{th}$ ,  $100^{th}$ , and  $150^{th}$  SC cycle. Within each SC event, the decreased SC drain current  $I_{\rm D}$  is a result of the significantly high SC current induced junction temperature  $T_{\rm i}$  increase [4] and the subsequent 2DEG mobility reduction [8]. In addition, the peak SC I <sub>D</sub> reduced from 55.2 to 45.1 A due to the positive shift of V th. Besides, the increased T i may also result in gate leakage increase during the SC event [7], which leads to a higher voltage drop across the resistor ( $R_{\rm G}$ ) connected to the gate terminal as shown in Fig. 1 (a). As a result, the SC waveform of  $V_{\rm GS}$  exhibits a moderate decrease within a single SC event as can be seen in Fig. 2 (b). On the other hand, together with the evolution of the repetitive SC cycles, the consistent trap filling in the gate region results in suppressed gate leakage which leads to a reduced voltage across  $R_{\rm G}$  and then a higher effective gate bias is applied at the gate terminal of the device. Hence, the  $V_{\rm GS}$  at the end point of the  $V_{\rm GS}$  SC waveform exhibits a marginal increase (see Fig. 2 (b)). The repetitive SC experiments are conducted on DUT1, 2, 3 and 4 at V  $_{\rm GS}$  =6 V, T  $_{\rm SC}=10 \ \mu s$ , and varied  $V_{\rm DD}=40 \ V$ , 50 V, 60 V and 70 V, respectively. Fig.3 (a) shows the transfer curves of DUT4. It can be seen that the transfer characteristic exhibits a substantial positive shift which leads to the  $V_{\rm th}$  (defined at  $I_{\rm DS}=1$  mA) significantly shifted from 1.22 V in the fresh device to 1.90 V after SC stress. Fig. 3 (b) plots the  $\Delta V_{\rm th}$  of DUT 1<sup>-4</sup> versus the SC cycles. The  $\Delta V_{\rm th}$  increases with the increasing SC cycles and gradually saturates for SC cycles >120. Moreover, with the identical SC stress cycles, the device exhibits higher  $\Delta V_{\rm th}$  stressed with higher V <sub>DD</sub>. Even though exhibiting substantial V <sub>th</sub> instability, all of the 4 tested devices were not failed after 150 SC cycles that suggests the strong repetitive SC capability of the devices, which is quite different from the reported 650 V Schottky p-GaN gate HEMTs featuring weak repetitive SC capability [4]. However, it should be pointed out that the significantly positive  $V_{\rm TH}$  shift

may induce an insufficient turn-on of GaN HEMTs as well as additional turn-on loss, which is detrimental to achieve high power efficiency of GaN HEMTs particularly for the low voltage GaN HEMTs that is supposed to operate at higher frequency where the switching loss is crucial for the power circuits.

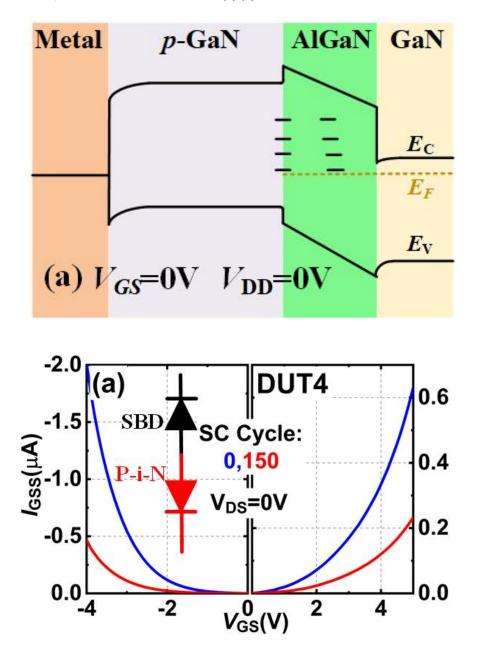

Fig.4 compares the typical gate leakage current  $I_{\text{GSS}}$  and off-state drain leakage current  $I_{\text{DSS}}$  of DUT-4 before and after SC stress.  $I_{\text{GSS}}$  is measured with source/drain terminal grounded, while  $I_{\text{DSS}}$  is measured in offstate with V GS=0 V. In positive gate bias, the applied voltage mainly drops across the upper metal/p-GaN Schottky diode in reverse mode, which facilitates blocking the gate leakage. In contrast, in negative gate bias, the upper Schottky diode is biased in forward mode that enables hole current conduction. Meanwhile, the applied gate voltage mainly drops across the p-i-n diode in reverse mode, which leads to higher reverse leakage by trap-state assistant electron tunneling due to the presence of trap states at p-GaN/AlGaN interface (e.g. N-vacancy or Ga-dangling bond) [9], [13] and in AlGaN barrier induced by Mg-dopant out-diffusion [10], [12]. Hence, the overall reverse gate leakage is higher than that in forward. Moreover, it can be seen that the  $I_{\rm GSS}$  exhibits a reduction after SC stress. Because the positive gate bias during the SC stress can sufficiently lower the p-GaN/AlGaN barrier, the significantly high SC current flows through the device with a large amount of 2DEG accumulated at the AlGaN/GaN interface channel. Meanwhile, the respectable large potential difference between gate and drain during SC event may result in a high electric-field located at the drain-side gate edge [4]. In this manner, driven by the locally high electric-field part of the high-density electrons in the channel can leap over the lowered energy barrier or tunneling through p-GaN/AlGaN gate stack, which leads to the increased gate leakage during the SC event and the simultaneous electron trapping by interface states at the p-GaN/AlGaN interface [11] and bulk traps in AlGaN barrier as depicted in Fig. 5. After occurrence of the electron-trapping, the interface states and bulk states filled with electrons are negatively charged, which tends to deplete the 2DEG in the channel and then results in positive shift in Vth. The trap states are gradually filled along with the increasing SC cycles. Hence, the  $\Delta V$  the increases with the SC cycles and then exhibits a saturation trend as observed in Fig. 3. Besides, the negatively charged traps can effectively suppress the gate leakage after stress as observed in Fig. 4 (a). Fig. 4 (b) shows the drain leakage  $I_{\rm DSS}$  and gate leakage  $I_{\rm G}$  in off-state measured before and after SC stress of DUT4. The identical  $I_{\rm DSS}$  and  $I_{\rm G}$  suggests that the off-state leakage of the device is dominated by the drain-to-gate leakage. More importantly, similar to  $I_{\rm GSS}$  measured in Fig 4(a), the off-state  $I_{\rm DSS}$  as well as  $I_{\rm G}$  show an obvious reduction after SC stress as shown in Fig. 4 (b), which reinforces that the occurrence of electron trapping in the p-GaN gate stack rather than in GaN buffer beneath the 2DEG channel.

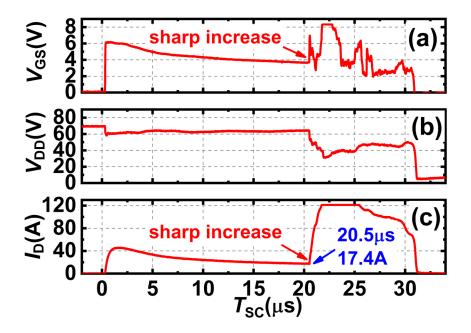

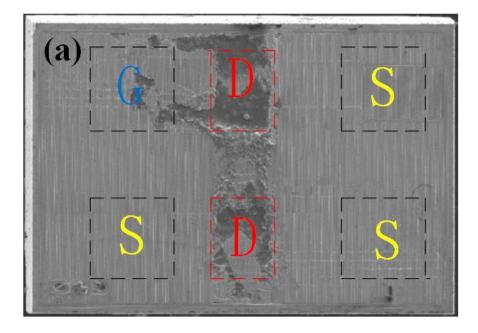

As the devices (i.e. DUT1<sup>4</sup>) were not failed, more stringent stress was further used to investigate the device failure mechanism. The DUT5 was stressed at  $V_{\rm GS}=6$  V,  $V_{\rm DD}=70$  V with a larger SC pulse duration of  $T_{\rm SC}=20$  µs. DUT5 failed within the 16<sup>th</sup> SC cycle with the SC waveform as shown in Fig. 7. It can be seen that the SC current  $I_{\rm D}$  exhibits an abrupt increase at 20.5 µs. The failed device behaves as the typical electrical shorting behavior between the drain and gate terminal. The failed device is then decapsulated and drain electrode burnout was observed in Fig. 8 (a). Since the SC current before the device failure is 17.4 A that is even lower than that as shown in Fig. 2 (b), the device failure is prone to be induced by the substantially high SC energy and its accumulation effect during the repetitive SC events (e.g. the 1<sup>st</sup> ~15<sup>th</sup>SC cycles) prior to eventual device failure.

We compare the SC energy  $(E_{\rm SC})$  of a single SC pulse of DUT-1<sup>-5</sup> as illustrated in Fig. 8 (b). It is worth noticing that  $E_{\rm SC}$  increases with the enhanced SC stress. Besides, the  $E_{\rm SC}$  of DUT1-4 are much lower compared with DUT-5 attributes to the longer  $T_{\rm SC}$ . More importantly, the much higher SC energy can cause a higher local temperature close to the drain electrode [3], [4]. The local temperature fluctuates between on-state and off-state in the repetitive SC cycles, generating cyclic mechanical stress of thermal expansion and contraction phases. Together with the repetitive SC events, the mechanical stress leads to accumulative degradation at drain electrodes during the  $1^{st}$  to  $15^{th}$  SC cycles. After that, in the  $16^{th}$  SC cycle, the accumulative degradation exceeds to a critical level and leads to fatigue failure and then the subsequent gate-to-drain short circuit with abrupt increase in SCI <sub>D</sub> as observed in Fig. 7(c). Consequently, the substantially high current results in the catastrophic thermal burned up of the two drain electrodes as shown in Fig. 8 (a).

Conclusion: The SC capability and device failure mechanism of the 100 V p-GaN gate HEMTs were investigated by the repetitive SC stress. In the repetitive SC stress with 150 SC cycles at  $V_{\rm GS}=6$  V,  $V_{\rm DD}=40^{\circ}70$  V and  $T_{\rm SC}=10$  µs, the device exhibits strong repetitive SC capability without device failure. However, significant positive shift in  $V_{\rm th}$  stems from electron trapping in the p-GaN/AlGaN gate stack is observed prior to the device failure. Accordingly, the electron-filled traps in turn to result in a suppressed gate leakage and off-state drain leakage current in the device after SC stress. By further enhancing the SC stress condition with a larger SC duration of 20 µs, the device can withstand ~15 cycles at  $V_{\rm GS}=6$  V and  $V_{\rm DD}=70$  V. The resultant significantly higher SC energy leads to thermal fatigue crack formation at the drain electrode due to the local temperature fluctuations, which results in the consequent thermal burnout.

Acknowledgements: This work was supported in part by National Natural Science Foundation of China under Grant 62174019, in part by the Guangdong Basic and Applied Basic Research Foundation, China under Grant 2019A1515011522 and 2021B1515140039, in part by the Zhuhai Industry-University Research Cooperation Project under Grant ZH22017001210041PWC.

## References

- X. Lyu, et al., "A Reliable Ultrafast Short-Circuit Protection Method for E-Mode GaN HEMT," IEEE Trans. on Power Electronics, vol. 35, no. 9, pp. 8926-8933, Sep. 2020, doi: 10.1109/TPEL.2020.2968865.

- E. A. Jones, et al., "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," *IEEE J.Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 707-719, Sep. 2016, doi: 10.1109/JESTPE.2016.2582685.

- S. Li *et al.*, "Understanding Electrical Parameter Degradations of P-GaN HEMT Under Repetitive Short-Circuit Stresses," *in IEEE Transactions on Power Electronics*, vol. 36, no. 11, pp. 12173-12176, Nov. 2021, doi: 10.1109/TPEL.2021.3077128.

- J. Sun, et al., "Short Circuit Capability Characterization and Analysis of p-GaN Gate High-Electron-Mobility Transistors Under Single and Repetitive Tests," in *IEEE Transactions on Industrial Electron*ics, vol. 68, no. 9, pp. 8798-8807, Sept. 2021, doi: 10.1109/ TIE.2020.3009603.

- C. Abbate, et al., "Failure analysis of 650 V enhancement mode GaN HEMT after short circuit tests," Microelectron. Reliab., vol. 88–90, pp. 677–683, Sep. 2018, doi: 10.1016/j.microrel.2018.07.071.

- M. Fernandez et al., "Short-circuit study in medium-voltage GaN cascodes, p-GaN HEMTs, and GaN MISHEMTs," *IEEE Trans. Ind. Electron*., vol. 64, no. 11, pp. 9012-9022, Nov. 2017, doi: 10.1109/TIE.2017.2719599.

- C. Pan, et al., "Physical Mechanism of Device Degradation Its Recovery Dynamics of p-GaN Gate HEMTs Under Repetitive Short Circuit Stress," 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2022, pp. 313-316, doi: 10.1109/ISPSD49238.2022.9813685.

- 8. N. Maeda, et al., "High-temperature electron transport properties in AlGaN/GaN heterostructures," Appl. Phys. Lett., vol. 79, no. 11, pp. 1634 1636, 2001, doi: 10.1063/1.1400779.

- 9. W. D. Callister, *et al.*, Materials Science and Engineering: An Introduction, 9th ed., Hoboken, NJ, USA: Wiley, 2014.

- Yang, M et al., "Electronic structure and optical properties of Al<sub>0.25</sub>Ga<sub>0.75</sub>N with point defects and Mg-defect complexes," Opt Quant Electron 50, 60 (2018), doi: 10.1007/s11082-018-1328-0.

- Yuanyuan Shi, et al., "Carrier Transport Mechanisms Underlying the Bidirectional V TH Shift in p-GaN Gate HEMTs Under Forward Gate Stress," *IEEE Trans. on Electron Devices*, vol. 66, no. 2, pp. 876-882, Feb. 2019, doi: 10.1109/TED.2018.2883573.

- P. Hacke, et al., "Deep levels in the upper band-gap region of lightly Mg-doped GaN," Appl. Phys. Lett., vol. 68, no. 10, pp. 1362–1364, Mar. 1996.

- A. C. et al., "AlGaN barrier thickness dependent surface and interface trapping characteristics of AlGaN/GaN heterostructure," Chinese Journal of Physics, vol.56, Issue 5, 2018, pp. 2365-2370, doi: 10.1016/j.cjph.2018.06.024.